Texas Instruments Microcontrôleurs (MCU) en temps réel TMS320F28P65x/TMS320F28P65x-Q1

Les Microcontrôleurs (MCU) en temps réel TMS320F28P65x/TMS320F28P65x-Q1 de Texas Instruments appartiennent à la famille C2000™ de microcontrôleurs en temps réel de dispositifs évolutifs à ultra-faible latence. Les MCU C2000 sont développés pour un rendement en électronique de puissance notamment, mais sans s'y limiter, pour des fréquences de densité de haute puissance et de commutation. De plus, ces dispositifs prennent en charge l’utilisation des technologies IGBT, GaN et SiC.Le sous-système de contrôle en temps réel des microcontrôleurs TMS320F28P65x/TMS320F28P65x-Q1 de TI est basé sur le cœur DSP C28x de 32 bits, qui offre 200 MIPS de performances de traitement du signal dans chaque cœur pour un code à virgule fixe ou flottante exécuté à partir d’une mémoire flash sur puce ou d’une SRAM. Les dispositifs TMS320F28P65x-Q1 sont qualifiés AEC-Q100 pour les applications automobiles.

Caractéristiques

- Traitement en temps réel

- Contient jusqu’à trois CPU : deux CPU DSP C28x 32 bits et un CPU CLA, tous fonctionnant à 200 MHz

- Fournit une puissance de traitement totale équivalente à un composant basé sur Arm® Cortex®-M7 1000 MHz sur des performances de chaîne de signal en temps réel

- Architecture DSP C28x

- Unité flottante (UVF) de précision double (64 bits) IEEE 754

- Unité de calcul trigonométrique (TMU)

- Division d'entier rapide (FINTDIV)

- Moteur CRC et instructions (VCRC)

- CPU d’accélérateur de loi de contrôle (CLA)

- IEEE 754 point flottant de précision simple

- Exécute le code indépendamment des processeurs C28x

- Sous-système analogique

- Trois convertisseurs analogique-numérique (CAN)

- Mode 16 bits, 1,19 MS/s chacun

- Mode 12 bits, 3,92 MS/s chacun

- Jusqu’à 40 entrées asymétriques ou 19 entrées différentielles

- Échantillonnage-blocage (S/H) séparé sur chaque CAN pour permettre des mesures simultanées

- Matériel après traitement des conversions

- Modes de suréchantillonnage (jusqu’à 128 fois) et de sous-échantillonnage matériel, avec accumulation, moyennage et rejet des valeurs aberrantes

- Quatre canaux d’entrée redondants pour plus de flexibilité

- Comparaison automatique des résultats de conversion pour les applications de sécurité fonctionnelle

- Onze comparateurs fenêtrés avec des références de convertisseur numérique-analogique (CNA) 12 bits

- CNA avec compensation de pente, permettant un contrôle du mode courant de crête et du courant de creux

- Options de connexion pour capteur de température interne et référence CAN

- Deux sorties CNA à tampon de 12 bits

- Deux réseaux de contrôleurs CAN FD/MCAN avec débit de données flexible

- Trois convertisseurs analogique-numérique (CAN)

- Périphériques de système

- Deux contrôleurs DMA (Direct Memory Access) à 6 canaux

- 185 broches d’entrée/sortie à usage général multiplexées programmables individuellement (GPIO)

- Contrôleur d'interruption périphérique étendu (ePIE)

- Prise en charge du mode basse consommation (LPM)

- Analyse et diagnostic intégrés en temps réel (ERAD)

- CRC de fond (BGCRC)

- Périphériques de sécurité

- Accélérateur standard de cryptage avancé (AES-128, 192, 256)

- Sécurité

- JTAGLOCK

- Démarrage à broche nulle

- Sécurité à double zone

- Numéro d'Identification unique (UID)

- Périphériques de sécurité

- Implémentation plus facile avec comparaison réciproque

- Verrouillage sur CPU C28x

- Alimentation mémoire sur auto-test (MPOST)

- Autotest matériel intégré (HWBIST)

- Conforme à la sécurité fonctionnelle ciblée

- Développé pour les applications de sécurité fonctionnelle

- Une documentation sera disponible pour aider à la conception de systèmes CEI 61508 et ISO 26262

- Capacité systématique jusqu'à ASIL D et SIL 3 ciblé

- Capacité matérielle jusqu'à ASIL B et SIL 2 ciblée

- Certification liée à la sécurité

- Certification ISO 26262 et CEI 61508 jusqu'à ASIL B et SIL 2 par TÜV SÜD prévue

- Contrôle de système et horloge

- Deux oscillateurs internes de 10 MHz

- Oscillateur à quartz sur puce

- RAM avec vecteur d'interruption redondant, BOR, 2*APLL

- Module de minuteur watchdog fenêtré

- Circuit de détection d'horloge manquante

- Comparateur à double horloge (DCC)

- Mise à jour du micrologiciel en direct (LFU)

- Passage rapide du contexte de l’ancien au nouveau micrologiciel avec ou sans cycle d’alimentation

- Noyau1,2 V, conception d'E/S 3,3 V

- VREG interne pour génération de 1,2 V

- Circuit de réinitialisation de baisse de tension (BOR)

- Mémoire

- 1,28 Mo de mémoire flash mappable CPU (protégé ECC) avec cinq bancs de mémoire flash

- 248 Ko de RAM (protection de parité améliorée)

- Interface mémoire externe (EMIF) avec ASRAM, prise en charge SDRAM ou ASIC/FPGA

- Périphériques de contrôle

- 36 canaux de modulateur de largeur d’impulsion (PWM), tous avec une capacité haute résolution de 150 ps (HRPWM)

- Logique de bande morte minimale (MINDB), logique de combinaison non autorisée (ICL) et autres fonctionnalités spéciales (c’est-à-dire la prise en charge de l’émulation de diode [DE])

- Activer les convertisseurs matriciels, les convertisseurs à niveaux multiples et les convertisseurs résonants prennent en charge sans logique externe supplémentaire

- Sept modules de capture améliorée (eCAP)

- La capture haute résolution (HRCAP) est disponible sur deux des sept modules eCAP

- Deux nouvelles unités de surveillance pour le bord, la largeur d’impulsion et la période qui peuvent être couplées aux stroboscopes ePWM et aux événements de déclenchement

- 256 entrées supplémentaires pour plus d’options de capture

- Nouvelle capacité de génération de SOC CAN

- L’eCAP peut également être utilisé pour des PWM supplémentaires

- Six modules d’impulsion d’encodeur en quadrature amélioré (eQEP)

- 16 canaux d’entrée du Module de filtre Sigma-Delta (SDFM), deux filtres indépendants par canal

- Générateur de modèles intégrés (EPG)

- Bloc logique configurable

- Six dalles logiques pour augmenter la capacité périphérique existante ou définir une logique personnalisée pour réduire ou supprimer le CPLD/FPGA externe

- Prend en charge les interfaces d’encodeur sans besoin de FPGA

- Permet une génération PWM personnalisée pour la conversion de puissance

- 36 canaux de modulateur de largeur d’impulsion (PWM), tous avec une capacité haute résolution de 150 ps (HRPWM)

- Périphériques de communication

- Contrôleur de dispositif subordonné (ou sous-dispositif) EtherCAT®

- USB 2.0 (MAC + PHY)

- Interface série rapide (FSI) permettant un échange de données jusqu’à 200 Mb/s à travers l’isolation

- Quatre ports SPI haut débit (jusqu’à 50 MHz)

- Quatre Interfaces de communication série (SCI) (prend en charge UART)

- Deux récepteurs/émetteurs asynchrones universels (UART) haut débit (25 Mbit/s)

- Deux interfaces I2C (400 ko/s)

- Option de démarrage externe via SPI/SCI/I2C

- Deux modules de réseau local d’interconnexion (LIN) compatibles UART (prise en charge SCI)

- Interface de Bus de gestion de puissance (PMBus) (prend en charge I2C)

- Un contrôleur de zone de réseau (CAN/DCAN)

- Options de boîtier :

- Emballage vert, sans plomb

- Nouvelle matrice de billes à pas fin (nFBGA) 256 billes [suffixe ZEJ], 13 mm × 13 mm / pas de 0,8 mm

- PowerPAD 176 broches = boîtier plat quadruple profil mince endurci thermiquement (HLQFP) [suffixe PTP], 26 mm × 26 mm / pas de 0,5 mm

- Nouvelle matrice à billes à pas fin (nFBGA) 169 billes [suffixe NMR], 9 mm × 9 mm / pas de 0,65 mm

- PowerPAD à 100 broches finement endurci thermiquement

- Pack plat quadruple (HTQFP) [suffixe PZP], 16 mm × 16 mm / pas de 0,5 mm

- Température ambiante (TA) de -40 à 125 °C (homologué pour l’industrie et l’automobile)

Applications

- Module de commande de servomoteur

- Asservissement de robots

- Contrôle CNC

- Commande de moteur robot mobile

- Contrôle de moteur commercial de grande taille CVC

- Contrôleur de segment de moteur linéaire

- Onduleur central

- Inverseur de chaîne

- Système de Conversion de puissance

- Station de chargement rapide CC

- Contrôle d'onduleur et de moteur

- CA-CC industriel

- ASI triphasés

- Onduleurs monophasés en ligne

- PSU serveur et réseau de commerçants

- Chargeur embarqué (OBC) et sans fil

- Module de compresseur CVC automobile

- Phare

Fiches techniques

Vidéos

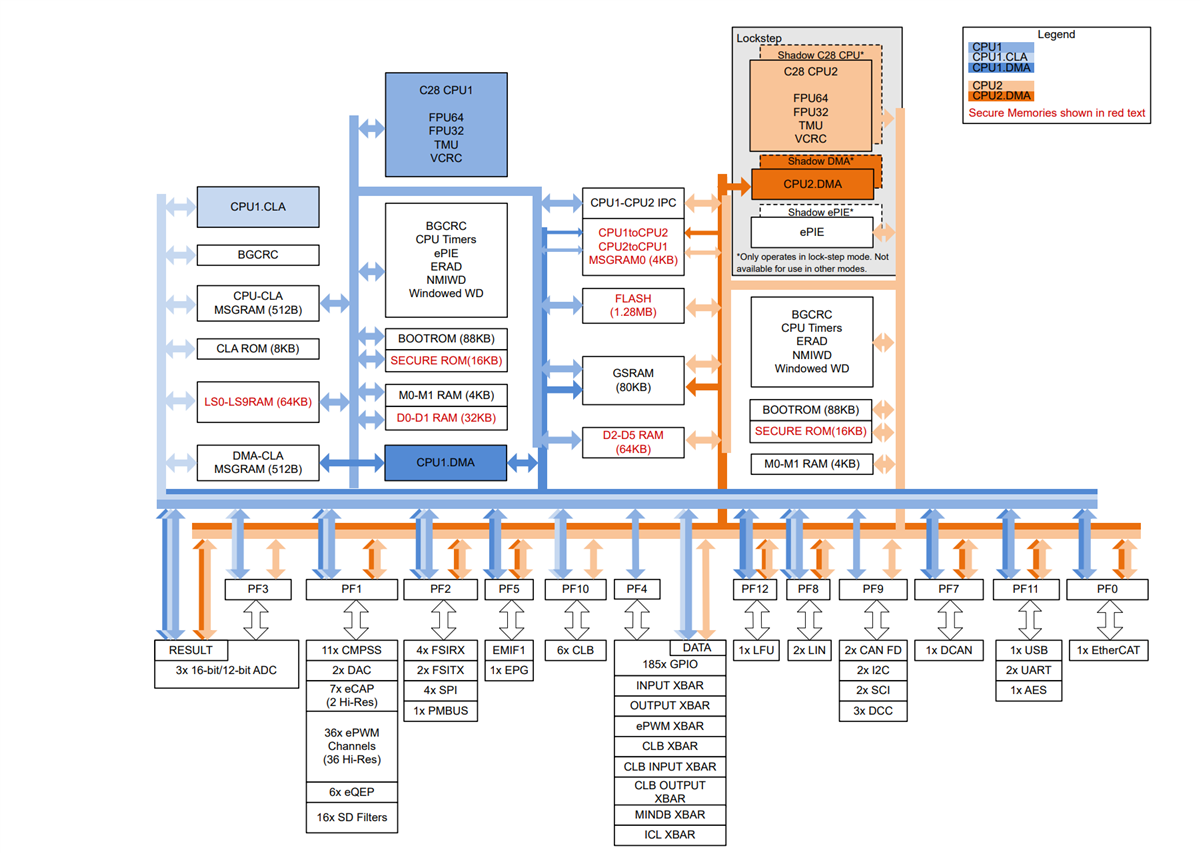

Schéma fonctionnel

Publié le: 2023-12-28

| Mis à jour le: 2026-02-06