Texas Instruments Émetteur-récepteur de bus SN74AVC1T45/SN74AVC1T45-Q1

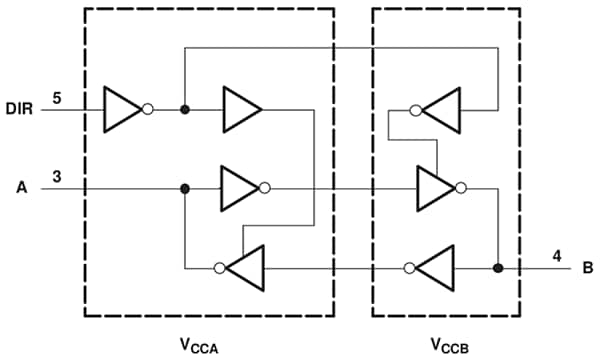

L'émetteur-récepteur de bus SN74AVC1T45/SN74AVC1T45-Q1 de Texas Instruments est un émetteur-récepteur de bus à un seul bit, non inverseur, utilisant deux rails d'alimentation configurables. Le SN74AVC1T45/SN74AVC1T45-Q1 fonctionne avec VCCA/VCCB de seulement 1,08 V. Le port A est conçu pour suivre VCCA. La VCCA accepte toute tension d'alimentation comprise entre 1,08 V et 3,6 V. Le port B est conçu pour suivre VCCB. La VCCB accepte toute tension d'alimentation comprise entre 1,08 V et 3,6 V. Cette caractéristique permet une conversion universelle bidirectionnelle à basse tension entre les nœuds de tension 1,2 V 1,5 V 1,8 V 2,5 V et 3,3 V.Le SN74AVC1T45/SN74AVC1T45-Q1 est conçu pour la communication asynchrone entre deux bus de données. Les niveaux logiques de l'entrée de contrôle de direction (DIR) activent soit les sorties du port A, soit les sorties du port B. Lorsque les sorties du port B sont activées, l'appareil transmet les données du bus A au bus B. Si les sorties du port A sont activées, l'appareil transmet du bus B au bus A. Les circuits d'entrée des ports A et B sont toujours actifs. Il doit appliquer un niveau logique HAUT ou BAS pour éviter un excès d'ICC et d'ICCZ.

Le SN74AVC1T45/SN74AVC1T45-Q1 de Texas Instruments est conçu pour que l'entrée DIR soit alimentée par la VCCA. Ce dispositif est entièrement spécifié pour les applications de mise hors tension partielle utilisant Ioff. Lors de la mise hors tension, la circuiterie Ioff désactive les sorties, évitant ainsi d'endommager le courant de retour. La fonction d'isolation VCC est conçue de telle sorte que si l'une des entrées VCC est à GND, les deux ports sont en état d'impédance élevée. La technologie de boîtier NanoFree utilise la puce comme boîtier et constitue une percée dans les concepts d'emballage des circuits intégrés.

Caractéristiques

- Disponible dans le boîtier NanoFree™ de Texas Instruments

- Une conception à double rail entièrement configurable permet à chaque port de fonctionner sur l'ensemble de la plage d'alimentation 1,08 V à 3,6 V.

- Fonction d'isolation VCC : si l'une des entrées VCC est à GND, les deux ports sont en état d'impédance élevée.

- Circuit d'entrée DIR référencé à VCCA

- Entraînement de la sortie de ±12 mA à 3,3 V

- Les E/S sont tolérantes à 4,6 V

- Ioff prend en charge un fonctionnement en mode de mise hors tension partielle

- La performance de verrouillage dépasse 100 mA selon JESD 78, classe II

- Débits de données maximaux standard

- 500 Mbps (conversion de 1,08 V à 3,3 V)

- 320 Mbps (conversion < 1,8="" v="" à="" 3,3="">

- 320 Mbps (conversion vers 2,5 V ou 1,8 V)

- 280 Mbps (conversion vers 1,5 V)

- 240 Mbps (traduire en 1,2 V)

- La protection ESD dépasse JESD 22

- Modèle de corps humain ±2000 V (A114-A)

- Modèle machine 200 V (A115-A)

- Modèle de l'appareil chargé ±1 000 V (C101)

Applications

- Électronique personnelle

- Industriel

- Entreprise

- Télécommunications

Schéma logique (logique positive)