Microchip Technology Microcontrôleurs (MCU) de sécurité avancés PIC32CX SG41/SG61

Les microcontrôleurs (MCU) de sécurité avancée PIC32CX SG41/SG61 de Microchip Technology sont des microcontrôleurs (MCU) à hautes performances, à processeur de 32 bits Arm® Cortex®-M4 et à Unité à virgule flottante (UVF). Ces dispositifs atteignent 120 MHz, 1 Mo de mémoire Dual Panel Flash avec conducteur de masse (ECC) et 256 ko de mémoire SRAM avec ECC. Ils ajoutent également un MAC Ethernet de 10/100 et 2 ports CAN-FD destinés à l'automatisation industrielle, aux applications automobiles et aux applications polyvalentes nécessitant une connectivité filaire. La mémoire flash comporte une région OTP utilisée pour développer un démarrage sécurisé et immuable. Elle offre également des fonctionnalités de débogage sécurisé, de protection contre l'effacement de puces, de protection d'IP et de protection de démarrage.Les microcontrôleurs (MCU) Microchip Technology de série PIC32CX SG41/SG61 offrent d'excellentes fonctionnalités, avec des performances de puissance hors pair et une sécurité matérielle intégrée.

Caractéristiques

- Cœur

- UCT / CPU Arm Cortex-M4F fonctionnant jusqu'à 120 MHz

- Cache d'instructions et cache de données combinés de 4 ko

- Unité de protection de la mémoire (MPU) 8 zones

- Unité à virgule flottante (FPU)

- Mémoires

- Mémoire flash auto-programmable dans le système 1 Mo avec code de correction d'erreur (ECC)

- Mémoire principale SRAM 256 ko avec code de correction d'erreur (ECC)

- Jusqu'à 4 ko de mémoire étroitement couplée (TCM)

- SRAM de sauvegarde supplémentaire de 8 ko

- Faible puissance et gestion de l'alimentation

- Modes de veille : inactif, veille, veille prolongée, sauvegarde et arrêt

- Périphériques SleepWalking

- Prise en charge de batterie de secours

- Sécurité

- Un système de cryptage avancé (AES) avec une longueur de clé de 256 bits et un débit de données pouvant atteindre 2 Mo/s

- Modes de fonctionnement BCE, CBC, CFB, OFB, CTR

- Générateur de nombres réellement aléatoires (TRNG)

- Contrôleur de cryptographie à clé publique (PUKCC)

- RSA, DSA

- Cryptographie des courbes elliptiques (ECC) ECC GF(2n), ECCGF(p)

- Module de contrôle de l'intégrité (ICM) basé sur un algorithme de hachage sécurisé (SHA1, SHA224, SHA256), assisté DMA

- Protection permanente contre l'effacement de puce, la programmation de section de démarrage et l'accès au débogage, permettant une section de démarrage immuable à taille configurable, une mémoire flash avec protection de lecture de démarrage, permettant une prise en charge du démarrage sécurisée

- Périphériques/minuteurs

- Système d'événements à 32 canaux

- Jusqu'à huit interfaces de communication série (SERCOM) configurables

- Huit minuteurs/compteurs (TC) 16 bits, chacun configurable en tant que TC 16 bits, 8 bits et 32 bits

- Deux minuteurs/compteurs 24 bits pour le contrôle (TCC) avec des fonctions étendues

- Trois minuteurs/compteurs 16 bits pour contrôle (TCC) avec fonctions étendues

- Compteur temps réel (RTC) 32 bits avec fonction horloge et calendrier

- Jusqu'à 5 broches de réveil avec détection d'intégrité et filtre anti-rebond

- Analogique avancé

- Double convertisseur analogique-numérique (CAN) 12 bits, 1 MS/s avec jusqu'à 16 canaux chacun

- Double convertisseur analogique-numérique (CAN) 12 bits, 1 MS/s avec jusqu'à 16 canaux chacun

- Deux comparateurs analogiques (AC) avec fonction de comparaison de fenêtre

- Interfaces de communication

- Une interface audio inter-CI (I2S) à deux canaux

- Contrôleur de capture parallèle (PCC), jusqu'à 14 bits de large

- Contrôleur tactile périphérique (PTC) avec jusqu'à 32 canaux d'auto-capacité et jusqu'à 256 canaux de capacité mutuelle

- Deux contrôleurs hôtes SD/MMC (SDHC)

- Contrôleur d'accès direct à la mémoire (DMAC) 32 canaux

- Une interface périphérique série quadruple E/S (QSPI)

- Un MAC Ethernet 10/100 Mbit/s avec DMA dédié

- Deux CAN (Controller Area Networks) avec prise en charge des CAN 2.0A/CAN 2.0B et CAN-FD (ISO)

- Un bus série universel (USB) 2.0 pleine vitesse (12 Mbit/s) avec hôte intégré et fonction de périphérique

- Système/gestion de l'horloge

- Oscillateur à quartz 32,768 kHz (XOSC32K) avec détection de défaillance d'horloge

- Deux oscillateurs à quartz (XOSC) de 8 MHz à 48 MHz avec détection de défaillance d'horloge

- Oscillateur interne à ultra faible puissance 32,768 kHz (OSCULP32K)

- Réinitialisation à la mise sous tension (POR) et détection de baisse de tension (BOD)

- Assistance au développement de débogueur

- Interface de programmation et de débogage SWD (Serial Wire Debug) à deux broches

- Six points de rupture matériels et quatre points de surveillance de données

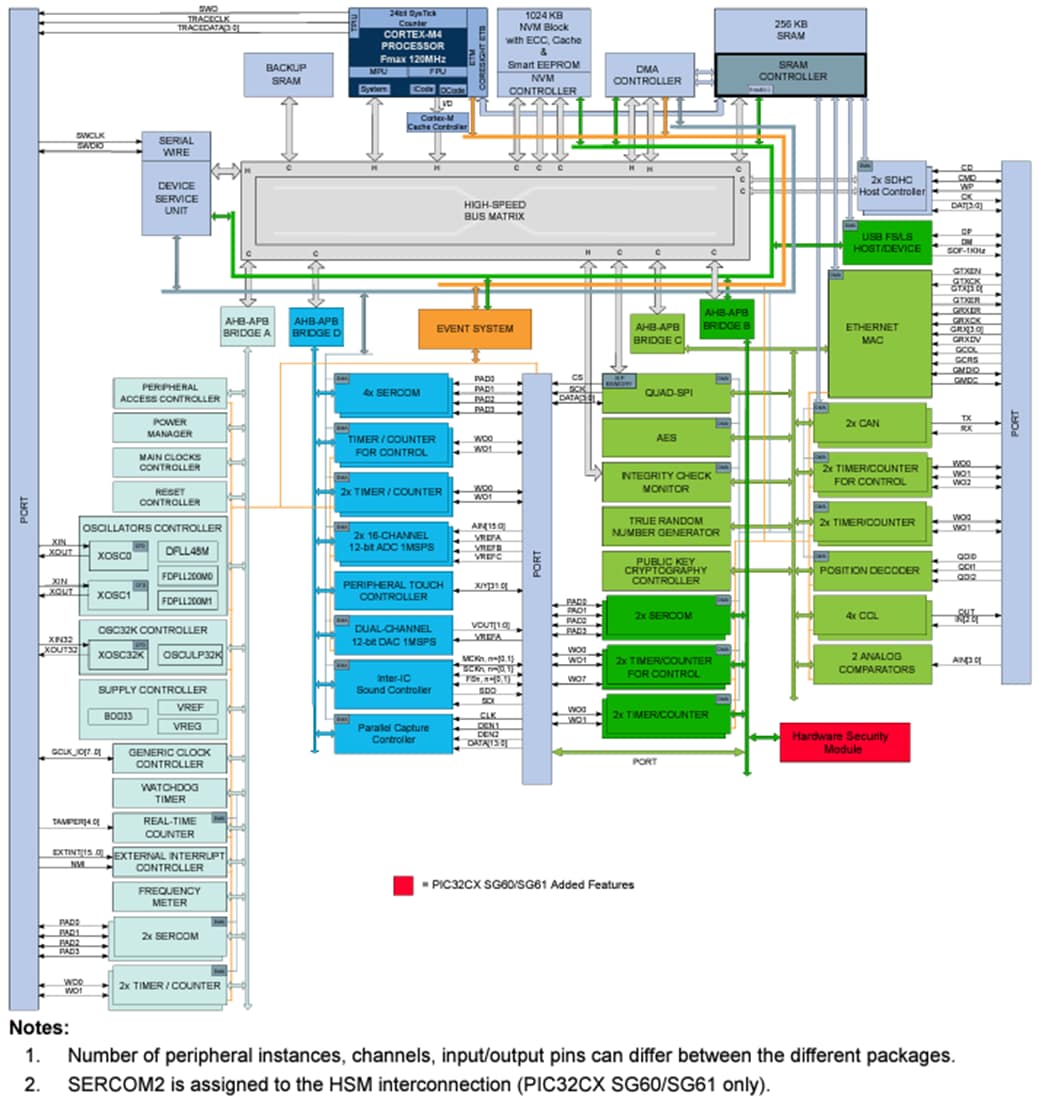

Schéma fonctionnel

Publié le: 2023-03-28

| Mis à jour le: 2025-02-24