Lattice Semiconductor Réseaux de portes programmables sur site MachXO4™

Les réseaux de portes programmables sur site (FPGA)MachXO4™ de Lattice Semiconductor étendent le portefeuille de FPGA Lattice Semiconductor à très faible densité avec des fonctionnalités avancées qui offrent flexibilité et efficacité. Les dispositifs MachXO4 combinent une faible consommation d’énergie, un flash intégré, une densité E/S élevée et une capacité d’activation instantanée. Grâce à une densité E/S exceptionnelle dans des boîtiers compacts, le MachXO4 intègre des fonctions renforcées qui contribuent à minimiser le coût du système et son empreinte. La large capacité de programmation et le support natif des interfaces conformes aux standards de l’industrie font de ces FPGA une solution évolutive pour des applications de connectivité et de contrôle en constante évolution.La productivité en matière de conception est améliorée grâce au logiciel Lattice Radiant™ qui prend en charge les conceptions complexes et de grande échelle grâce à une synthèse RTL de pointe, une base de données de conception unifiée, des scripts avancés, une interface graphique moderne, une analyse de synchronisation et un analyseur logique intégré. Lattice propose également une large gamme de modules IP préconçus pour la famille MachXO4™.

Caractéristiques

- Variants (entièrement fonctionnels et brochage compatible)

- ZC - ultra-faible puissance, alimentation 2,5V/3,3V

- HC - haute performance, alimentation 2,5V/3,3V

- HE - haute performance, alimentation 1,2 V

- Construit sur un processus non volatile à faible consommation de 65 nm

- Consommation extrêmement faible, aussi basse que 140 µW en mode statique.

- Large plage de sélection de densité logique de 896 LUT à 9400 LUT

- Mémoire Flash intégrée avec Mémoire Flash utilisateur (UFM) jusqu’à 448 ko

- Jusqu’à 432 ko de blocs chargés dans la mémoire intégrée (EBR) et 54 ko de mémoire de RAM distribuée

- Mise sous tension instantanée avec un temps de démarrage rapide de moins de 5 ms

- Tampon hautement flexible prenant en charge les normes E/S 3,3 V et 1 V pour l’interconnexion des dispositifs existants et de nouvelle génération

- Sertissage à chaud avec un courant de fuite aussi faible que 350 µA et absence de séquencement de l’alimentation électrique

- Prise en charge des tensions mixtes pour les types d’E/S LVCMOS et LVTTL

- Résistances pull-down intégrées par défaut pour minimiser le nombre de composants externes

- Boîtiers compacts avec un rapport E/S par matrice LUT élevé, jusqu’à 382 broches E/S

- Fonctions SPI, I2C, minuteur/compteur et fonctions d'oscillateur renforcées sur puce

- Amélioration de la productivité de conception grâce au logiciel Lattice Radiant

- Conforme à la directive RoHS

Applications

- Calcul

- Serveurs de centres de données

- Réseaux et stockage

- Accélération matérielle

- Communications

- Commutateurs Ethernet et routeurs

- Accès large bande

- Unités radio

- Électronique grand public

- Écrans d'affichage

- Caméras

- Smartphones

- Industrie

- Contrôle de moteur

- Dispositifs portables

- Mesure et test

- Contrôleurs logiques programmables

- Automobile (pièces se terminant par A)

- Système d'aide à la conduite (ADAS)

- Convertisseurs

- Contrôle de moteur

- Infoloisir

- Gestion de batterie

Caractéristiques techniques

- Architecture programmable et faible puissance

- Densité logique allant de 896 à 9 400 LUT4

- De 64 ko à 432 ko de blocs chargés dans la mémoire intégrée (EBR)

- Jusqu’à 54 Ko de mémoire de RAM distribuée

- Logique de contrôle dédiée PEPS

- Processus avancé de faible puissance de 65 nm

- E/S différentiel programmable à faible amplitude

- Mode en veille et autres options d’économie d’énergie

- Tampon E/S flexible et hautement performant

- Le tampon programmable sysI/O™ prend en charge une large gamme d’ interfaces.

- LVCMOS 3,3/2,5/1,8/1,5/1,2/1,0

- LVTTL

- LVDS, Bus-LVDS, MLVDS, LVPECL

- MIPI D-PHY émulé

- Bascules (trigger) de Schmitt, hystérésis jusqu’à 0,5 V

- Prise en charge des prises à chaud E/S

- Terminaison différentielle sur puce

- Mode pull-up ou pull-down programmable

- Le tampon programmable sysI/O™ prend en charge une large gamme d’ interfaces.

- E/S synchrone de source pré-conçue

- Registres DDR dans les cellules E/S

- Logique de rapport dédiée

- Rapport 7:1 pour E/S écran

- DDR générique, DDRx2 et DDRx4

- Large gamme de boîtiers à technologies avancées

- Boîtiers compacts avec un rapport I/O-à-LUT élevé jusqu’à 382 broches E/S

- Pas de 0,4 mm - 1280 à 4320 LUT dans une empreinte WLCSP très petite (2,5 mm × 2,5 mm à 3,8 mm × 3,8 mm) avec 27 à 62 E/S

- Pas de 0,5 mm - 896 à 4320 LUT dans des boîtiers BGA TQFP de 8 mm x 8 mm à 20 mm x 20 mm avec jusqu’à 112 E/S

- Pas de 0,8 mm - 1280 à 9400 LUT dans des boîtiers BGA de 14 mm x 14 mm à 19 mm x 19 mm avec jusqu’à 382 E/S

- Pas de 1.0 mm - LUTs 1280 à 4320 dans un boîtier BGA 17 mm x 17 mm avec 204 E/S

- Non volatile, reconfigurable plusieurs fois

- Démarrage instantané en quelques millisecondes

- Double démarrage en option avec mémoire SPI externe

- Solution sécurisée à puce unique

- Programmable via JTAG, SPI ou I2C

- Mémoire Flash reconfigurable jusqu’à 100 000 cycles d’écriture/effacement pour les dispositifs à usage commercial/industriel et 10 000 cycles d’écriture/effacement pour dispositifs automobiles

- Prend en charge la programmation en arrière-plan de la mémoire non volatile

- Mise à jour logique sur site tandis que les E/S maintiennent l’état du système grâce à la reconfiguration TransFR

- Horlogerie optimisable sur puce

- Oscillateur sur puce avec une précision de 5,5 % pour les dispositifs commerciaux/industriels

- 8 horloges principales

- Jusqu’à deux horloges de bord pour les interfaces E/S haut débit, côtés haut et bas uniquement

- Jusqu’à deux PLL analogiques par dispositif avec synthèse de fréquence fractionnaire-n

- Large plage de fréquence d’entrée de 7 MHz à 400 MHz

- Prise en charge améliorée au niveau du système

- Fonctions renforcées sur puce - SPI, I2C, et minuteur/compteur

- TraceID unique pour le suivi du système

- Alimentation électrique unique avec plage de fonctionnement étendue

- Norme IEEE standard 1 149.1 sur le balayage des limites

- Programmation intégrée conforme à la norme IEEE 1532

- Logiciel de conception à la pointe de la technologie

- Le dispositif MachXO4 est pris en charge dans Lattice Radiant

- Prise en charge du langage RTL leader du secteur pour VHDL, VHDL-2008, Verilog et SystemVerilog

- Capacité d’écriture avancée sur la ligne de commande et flux de conception TCL

- Flux de compilation en un clic et sondage croisé entre les outils d’analyse

- Analyseur de synchronisation et de logique intégré

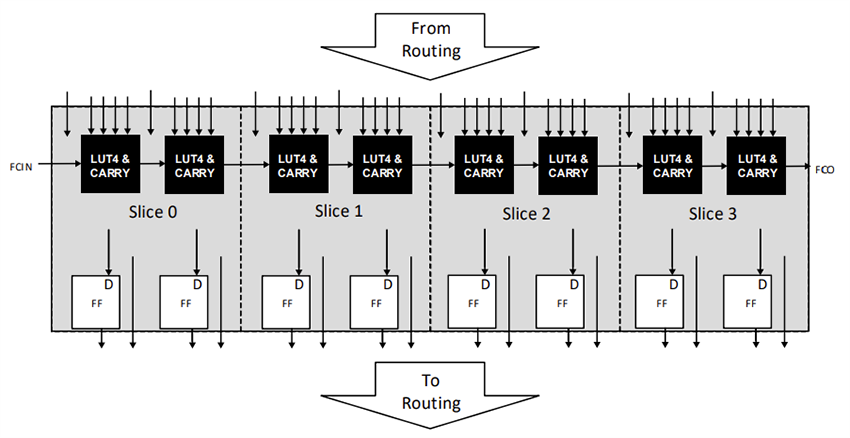

Schéma fonctionnel PFU

Le cœur du dispositif MachXO4 est constitué de blocs PFU, qui peuvent être programmés pour effectuer des fonctions logiques, arithmétiques, de mémoire RAM distribuée et de fonctions ROM distribuées. Chaque bloc PFU est composé de quatre tranches interconnectées numérotées de zéro à trois. Chaque tranche contient deux LUT et deux registres. Chaque bloc PFU est associé à 53 entrées et 25 sorties.

Schéma des tranches

Les tranches de zéro à trois contiennent deux LUT4 qui alimentent deux registres. Les tranches zéro à deux peuvent être configurées comme mémoire distribuée. La logique de contrôle effectue des fonctions de configuration/réinitialisation (programmable en synchrone/asynchrone), de sélection d’horloge, de sélection de puce et des fonctions RAM/ROM plus larges. Les registres de la tranche peuvent être configurés pour des horloges positives/négatives et à déclenchement ou sensibles au niveau. Toutes les tranches disposent de 15 entrées provenant du routage et une de la chaîne de transport (de la tranche adjacente ou PFU). Il y a sept sorties : six pour le routage et une pour la chaîne de transport (vers la PFU adjacente).

Schéma PLL

Le MachXO4 BVP contient un port caractéristique WISHBONE qui permet de modifier dynamiquement les paramètres BVP ainsi que les valeurs de diviseur, à partir de la logique utilisateur. Lors de l’utilisation de cette caractéristique, le bloc EFB doit également être instancié dans la conception pour permettre l’accès aux ports WISHBONE. De même que pour le réglage dynamique de la phase, lorsque les paramètres BVP sont mis à jour via le port WISHBONE, le BVP peut perdre le verrouillage et ne pas se reverrouiller tant que le paramètre tLOCK n’est pas satisfait.