Analog Devices Inc. Double synchroniseur d'horloge numérisée DPLL AD9546

Le double synchroniseur d'horloge numérisé DPLL AD9546 d'Analog Devices Inc. combine une technologie d'horloge numérisée qui transporte et distribue efficacement les signaux d'horloge dans les systèmes. L'horloge numérisée sur l'AD9546 permet de concevoir des systèmes de transport d'horloge flexibles et évolutifs avec un alignement de phase (temps) bien contrôlé. L'AD9546 est idéal pour la conception d'équipements réseau qui doivent répondre aux exigences de synchronisation des horloges frontière IEEE® 1588™ selon la classe D de ITU-T G.8273.2. De plus, l'horloge numérisée est également pertinente dans les applications nécessitant un transport précis de la fréquence et de la phase vers de multiples points de terminaison d'utilisation, tels que, la distribution d'horloges de référence de système synchronisé (SYSREF) à une variété de canaux CAN.Le double synchroniseur d'horloge numérisée AD9546 d'ADI prend en charge les normes existantes et émergentes de l'Union Internationale des Télécommunications (UIT) pour la livraison de la fréquence, de la phase et de l'heure du jour sur les réseaux de paquets des fournisseurs de services (ITU-T G.8262, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, et ITU-T G.8273.2).

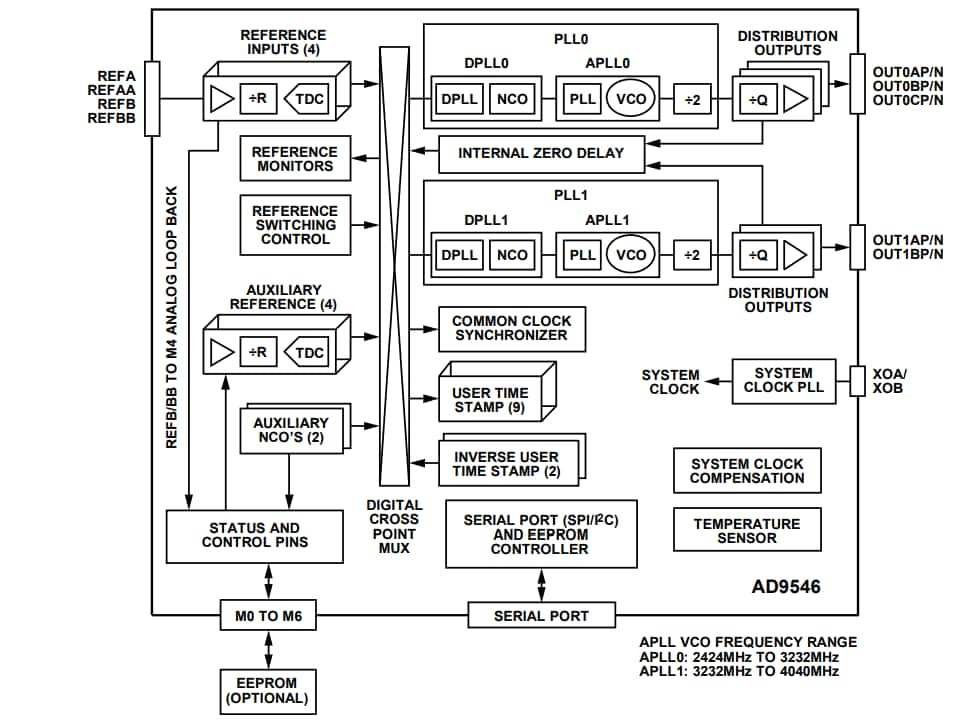

Le composant offre dix sorties d'horloge qui se synchronisent avec l'une des huit références d'entrée au maximum. Les boucles numériques à verrouillage de phase (DPLL) réduisent la gigue de synchronisation associée aux références externes et les boucles analogiques à verrouillage de phase (APLL) fournissent une traduction de fréquence avec des horloges de sortie à faible gigue. La boucle à commande numérique et le circuit rémanent génèrent en continu un signal de sortie à faible gigue, même lorsque toutes les entrées de référence font défaut.

L'AD9546 est logé dans un boîtier LFCSP (7 mm × 7 mm) à 48 fils et fonctionne sur la plage de température de -40 °C à +85 °C.

Caractéristiques

- Sous-système de transport d'horloge numérisé

- 9 blocs UTS indépendants (ports de sortie d'horodatage)

- 2 blocs d'IUTS indépendants (ports d'entrée à horodatage)

- Le double DPLL synchronise les horloges de couche physique de 1 Hz à 750 MHz, fournissant une traduction de fréquence avec un nettoyage de gigue des références bruyantes

- Conforme aux normes ITU-T G.8262 et Telcordia GR-253

- Prend en charge Telcordia GR-1244, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825 et ITU-T G.8273.2

- Surveillance continue de la fréquence et validation de référence pour une déviation de fréquence pouvant descendre à 50 ppb (5 × 10−8)

- Les deux DPLL disposent d'un diviseur fractionnaire de 24 bits avec un module programmable de 24 bits

- Bande passante de filtre de boucle numérique programmable : 0,0001 Hz à 1 850 Hz

- 2 NCO auxiliaires programmables et indépendants (1 Hz à 65 535 Hz, résolution <1,37 pHz), adaptés à IEEE 1588

- Rétroaction servo version 2 dans les applications PTP

- Commutation de référence et maintien automatique et manuel, fournissant un fonctionnement sans délai, sans contact ou sans phase

- Commutation de référence programmable basée sur les priorités avec modes manuel, réversible automatique et non-réversible automatique pris en charge

- 5 paires de broches de sortie d'horloge avec chaque paire utilisable comme LVDS/HCSL/CML différentiel ou comme 2 sorties asymétriques (1 Hz à 500 MHz)

- 2 références d'entrée différentielles ou 8 références d'entrée asymétriques

- Le point de croisement de multiplexage connecte les entrées de référence aux PLL

- Prend en charge les signaux d'horloge d'entrée/sortie intégrés (modulés)

- Modes de verrouillage DPLL rapide

- Offre une capacité interne pour combiner le faible bruit de phase d'un résonateur à quartz ou d'un oscillateur à quartz avec la stabilité de la fréquence et

- la précision d'un TCXO ou OCXO

- Prise en charge EEPROM externe pour une initialisation autonome

- Fonctionnement d'une seule alimentation de 1,8 V avec régulation interne

- Moniteur de température intégré et compensation de l'alarme et de la température pour des performances de délai nul améliorées

Applications

- Synchronisation de haute précision de temps de transport 5G

- Système de positionnement global (GPS), protocole de temps de précision (PTP) (IEEE 1588) et nettoyage et synchronisation de gigue Ethernet synchrone (SyncE)

- Réseaux de transport optique (OTN), hiérarchie numérique synchrone (SDH) et stations de base macro et petites cellules

- Petite horloge de station de base (bande de base et radio)

- Maintien de Stratum 2, Stratum 3e et Stratum 3, nettoyage de gigue et contrôle transitoire de phase

- Prise en charge JESD204B pour horloge de convertisseur analogique-numérique (CAN) et de convertisseur numérique-analogique (CNA)

- Carrier Ethernet

Schéma fonctionnel