Lattice Semiconductor FPGA Mach-NX

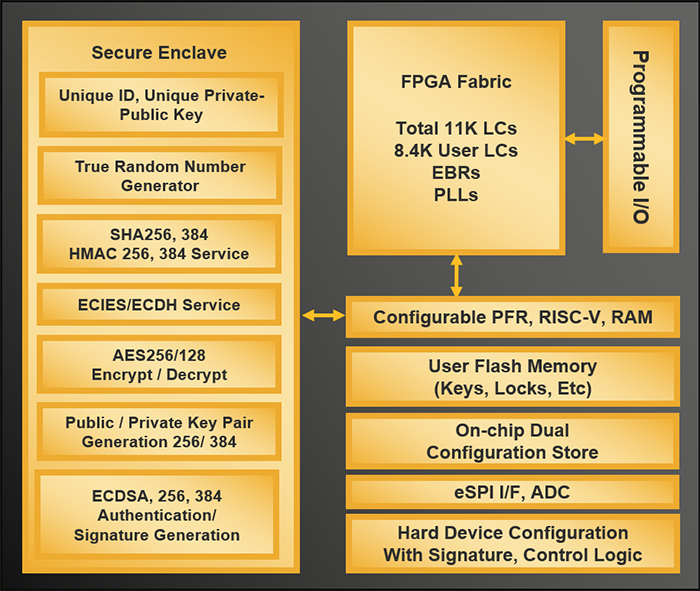

Les réseaux de portes programmables sur site Mach-NX de Lattice Semiconductor sont des FPGA à faible densité, comprenant des fonctions de sécurité améliorées et une mémoire flash à double démarrage sur puce composée de SoC et de partitions FPGA. Les caractéristiques de sécurité améliorées incluent la norme de cryptage avancée (AES) AES-128/256, l’algorithme de hachage sécurisé (SHA) SHA-256/384, l’algorithme de signature numérique à courbe elliptique (ECDSA), le système de cryptage intégré à courbe elliptique (ECIES), le code d’authentification de message de hachage (HMAC) HMAC-SHA256/384, la cryptographie à clé publique et l’identifiant sécurisé unique.Les FPGA Mach-NX combinent une enclave sécurisée (un moteur cryptographique matériel avancé de 384 bits prenant en charge une protection reprogrammable du flux binaire) avec une cellule logique (LC) et un bloc d'E/S. L’enclave sécurisée aide à sécuriser le micrologiciel et le bloc LC et E/S permettent des fonctions de contrôle du système telles que la gestion de l’alimentation et le contrôle du ventilateur. Les composants peuvent vérifier et installer des mises à jour de micrologiciels par liaison radio, en maintenant les systèmes conformes aux directives et protocoles de sécurité en évolution. L’architecture de traitement parallèle du FPGA Mach-NX et la configuration de mémoire flash à double démarrage fournissent les temps de réponse quasi-instantanés nécessaires pour détecter et récupérer des attaques (niveau de performance dépassant les capacités d’autres plateformes HRoT telles que les MCU).

Les dispositifs Mach-NX de Lattice Semiconductor sont une solution matérielle racine de confiance qui peut facilement s’étendre pour protéger l’ensemble du système avec une sécurité de flux binaire améliorée et des fonctions de mode utilisateur. Le composant Mach-NX prend en charge les toutes dernières E/S aux normes de l’industrie et fournit une densité d’E/S révolutionnaire avec un grand nombre d’options de programmabilité des E/S.

Caractéristiques

- Jusqu’à 8,4 K LC de logique utilisateur, 2669kbits de mémoire flash utilisateur et une fonction flash à double démarrage

- Jusqu’à 379 E/S programmables prenant en charge des tensions d’E/S 1,2/1,5/1,8/2,5/3,3

- L’enclave sécurisée prend en charge la cryptographie 384 bits, y compris SHA, HMAC et ECC

- La configuration des fonctions PFR et de sécurité via Lattice Propel simplifie l’expérience du développeur

- Haute fiabilité, faible consommation et performances SER 3 fois meilleures par rapport aux technologies CMOS comparables

Applications

- Démarrage sécurisé et racine de confiance

- Calcul et stockage

- Communications sans fil

- Systèmes de contrôle industriel

Caractéristiques techniques

- Solutions

- Meilleur FPGA de contrôle de sa catégorie avec fonctions de sécurité avancées, fournit un démarrage sécurisé/authentifié et une fonction racine de confiance

- Empreinte optimisée, densité logique, nombre d’E/S, dispositifs de performance E/S pour la gestion d’E/S et les applications logiques

- Dispositifs E/S élevés pour applications d’extension E/S

- Architecture flexible avec un rapport E/S élevé vers LC avec jusqu’à 379 broches E/S

- Enclave cryptographique sécurisée

- Norme de cryptage avancée (AES), chiffrement/décryptage AES-128/256

- Algorithme de hachage sécurisé (SHA), SHA-256/384

- Algorithme de Signature numérique à courbe elliptique (ECDSA), authentification basée sur ECDSA

- Code d’authentification de message de hachage (HMAC), HMAC-SHA256

- Schéma de cryptage intégré à courbe elliptique (ECIES), cryptage et décryptage ECIES

- Générateur de nombres réellement aléatoires (TRNG)

- Gestion des clés à l’aide de la cryptographie à clé publique Elliptic Curve Diffie-Hellman (ECDH)

- Identifiant sécurisé Unique

- Protège contre les attaques malveillantes

- Interface de boîte aux lettres vers bloc de fonction SoC

- Protocoles de sécurité pris en charge par la norme fédérale de traitement de l’Information (FIPS)

- Tampon E/S flexible et haute performance

- Le tampon sysI/O™ programmable prend en charge une large gamme d’interfaces sur certaines banques

- LVCMOS 3,3/2,5/1,8/1,5/1,2

- LVTTL

- LVDS, Bus-LVDS, MLVDS et LVPECL

- Entrées de déclenchement Schmitt, jusqu’à hystérésis 0,5 V

- Idéal pour les applications de pontage E/S

- Contrôles de vitesse de balayage lents/rapides

- Prise en charge des prises à chaud E/S

- Terminaison différentielle sur puce

- Mode pull-up ou pull-down programmable

- Le tampon sysI/O™ programmable prend en charge une large gamme d’interfaces sur certaines banques

- E/S synchrones source pré-conçues

- Registres DDR dans les cellules E/S

- Logique de rapport dédiée

- DDR générique, DDRx2 et DDRx4

- 5 entrées d’horloge primaire

- 8 lignes d’horloge primaires internes

- Oscillateur sur puce avec précision 5,5 %

- 2 PLL analogiques par dispositif avec synthèse de fréquence sous-fractionnée, large plage de fréquence d’entrée (7 MHz à 400 MHz)

- Balayage de limite standard IEEE 1149,1

- Programmation en système conforme IEEE 1532

- Non volatile, reconfigurable

- Instant-on

- UFM Multi-sections pour le stockage des données client

- Solution sécurisée à puce unique

- Programmable via JTAG, SPI ou I2C

- La mémoire flash reconfigurable prend en charge la programmation en arrière-plan d’une mémoire non volatile

- Reconfiguration TransFR, mise à jour logique sur le terrain tandis que les E/S conservent l’état du système sur certaines banques

- Bloc de fonction SoC

- Processeur RISC-V 32 bits avec RAM de micrologiciel sur puce et interface maître AHB-Lite

- Enclave cryptographique sécurisée

- Fonctions durcies sur puce

- SPI

- I2C

- Minuteur/compteur

- PFR

Schéma fonctionnel