Infineon Technologies Mémoire HYPERRAM™ 2,0 S27KS064x et S27KL064x

Les mémoires HYPERRAM™ 2.0 S27KS064x et S27KL064x d'Infineon Technologies sont des DRAM à haute vitesse et faible nombre de broches pour les systèmes intégrés à hautes performances nécessitant une mémoire d'extension. Ces dispositifs offrent des interfaces HYPERBUS™ et SPI octal qui s'appuient sur les caractéristiques héritées des mémoires d'interface parallèle et série. Ces DRAM fonctionnent sur une plage de tension de 1,8 V à 3 V et offrent une largeur de bande pouvant atteindre 400 Mbits/s. Cela fait de l'HYPERRAM™ 2.0 la mémoire d'extension idéale pour les contrôleurs ayant une RAM embarquée limitée. L'HYPERRAM™ 2.0, lorsqu'elle est utilisée comme mémoire bloc-notes, permet aux opérations de lecture et d'écriture de fournir rapidement des graphiques à haute résolution. Les applications typiques incluent les instruments de bord automobiles, l'interface homme-machine (IHM) industrielle, la vision industrielle et les systèmes d'affichage pour l'électronique grand public.Les DRAM HYPERRAM™ 2.0 S27KS064x et S27KL064x d'Infineon Technologies sont proposés en boîtier BGA (Ball Grid Array) renforcé.

Caractéristiques

- Technologie : DRAM 38 nm

- Interface HYPERBUS

- Prise en charge d’interface de 8 V à 3,0 V

- Signaux de bus à horloge asymétrique (CK) - 11

- Signaux de bus - 12 d’horloge différentielle (CK, CK#) optionnels

- Sélection de puce (CS#)

- Bus de données 8 bits (DQ[7:0])

- Réinitialisation matérielle (n° de réinitialisation)

- Course de données en lecture/écriture bidirectionnelle (RWDS)

- Sortie au début de toutes les transactions pour indiquer la latence de rafraîchissement

- Sortie pendant la lecture des transactions comme lecture de données stroboscopiques

- Saisie pendant les transactions d’écriture comme masque de données d’écriture

- Saut de lecture centre DDR optionnel (DCARS)

- Pendant les transactions de lecture, le RWDS est décalé par une seconde horloge, déphasée de CK

- L’horloge à décalage de phase est utilisée pour déplacer le bord de transition RWDS dans l’œil de lecture des données

- Fréquence d’horloge maximale 200 MHz

- DDR - transfère des données sur les deux bords de l’horloge

- Débit de données atteignant 400 Mbits/s (3 200 Mbits/s)

- Caractéristiques de rafale configurables, rafale linéaire

- Longueurs de rafales enveloppées

- 16 octets (huit horloges)

- 32 octets (16 horloges)

- 64 octets (32 horloges)

- 128 octets (64 horloges)

- Option hybride - une rafale enroulée suivie d’une rafale linéaire

- Puissance de pilotage de sortie configurable

- Modes de puissance

- Mode veille hybride

- Mise à l’arrêt

- Rafraîchissement de matrice

- Matrice mémoire partielle (1/8, 1/4, 1/2)

- Intégral

- Plage de température de fonctionnement

- Industriel (I) : -40 °C à +85 °C

- Industriel Plus : -40 °C à 105 °C

- Automobile, AEC-Q100 classe 3 : -40 °C à 85 °C

- Automobile, AEC-Q100 classe 2 : -40 °C à 105 °C

- Boîtier FBGA24 6,0 mm x 8,0 mm x 1,0 mm

Applications

- Consoles d’instruments

- Systèmes d’affichage pour l’électronique grand public

- IHM grand public et industriel

- Vision industrielle industrielle

Vidéos

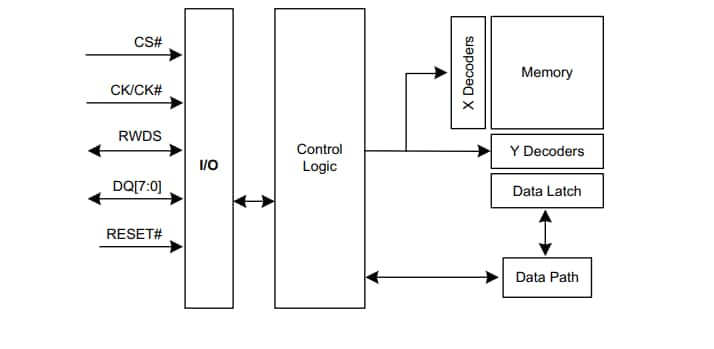

Schéma de principe logique

Publié le: 2020-02-24

| Mis à jour le: 2024-09-27