Analog Devices Inc. DSP SHARC+ double cœur ADSP-21591/ADSP-21593

Les DSP à double cœur SHARC+ ADSP-21591/ADSP-21593 d’Analog Devices Inc. font partie de la famille de processeurs de signal numérique (DSP) SHARC à instructions simples et données multiples (SIMD) qui disposent d’une architecture ADI Super Harvard. Les DSP ADSP-21591/ADSP-21593 sont optimisés pour les applications audio / à virgule flottante hautes performances avec grande mémoire d’accès aléatoire statique (SRAM) sur puce, plusieurs bus internes qui éliminent les goulets d’étranglement entrée/sortie (E/S) et des interfaces audio numériques innovantes (DAI). Ces composants sont des processeurs à virgule flottante 32 bits, 40 bits ou 64 bits. De plus, les dispositifs offrent des améliorations de cache et une prédiction de branche tout en maintenant la compatibilité du jeu d'instructions avec les produits SHARC précédents.Les DSP SHARC+ double cœur ADSP-21591/ADSP-21593 d'ADI intègrent un ensemble de périphériques système et de mémoire à la pointe de l'industrie, idéaux pour les applications qui nécessitent une programmabilité similaire à un calcul de jeu d'instructions (RISC) réduit, une prise en charge multimédia et un traitement du signal de pointe dans un seul boîtier. Ces applications couvrent un large éventail de marchés, notamment l'automobile, l'audio professionnel et les applications industrielles qui nécessitent de hautes performances en virgule flottante.

Caractéristiques

- Système

- Doubles cœurs à virgule flottante SHARC+ améliorés

- Cœurs SHARC+ haute performance (jusqu'à 1 GHz chacun)

- Mémoire SRAM L1 jusqu'à 5 Mo (640 ko) par cœur avec parité (possibilité optionnelle de configurer comme cache)

- Prise en charge de virgule flottante de 32 bits, 40 bits et 64 bits

- Prise en charge de virgule fixe 32 bits

- Adressabilité en octets, mots courts, mot et mots longs

- Cœur Arm Cortex-A5

- Jusqu'à 1 GHz/1 600 DMIPS avec NEON/VFPv4-D16

- Cache d'instructions et de données L1 de 32 ko avec parité

- Cache L2 256 ko avec parité

- Système DMA puissant avec des DMA 8 mémoires

- Protection de mémoire sur puce

- Caractéristiques de sécurité intégrées

- 17 mm × 17 mm, BGA_ED 400 billes (pas de 0,8 mm), conforme RoHS

- Mémoire

- Grande SRAM sur puce de niveau 2 (L2) avec protection ECC, jusqu'à 2 Mo

- Une interface de niveau 3 (L3) fournissant une interface 16 bits aux dispositifs SDRAM DDR3 / DDR3L

- Généralités

- Options de boîtier compatible avec les broches ADSP-2156x

- Accélérateurs FIR et IIR améliorés fonctionnant jusqu'à 1 GHz

- Sécurité et protection

- Accélérateurs matériels cryptographiques

- Amorçage sécurisé rapide avec protection IP

- Prise en charge de Arm TrustZone

Applications

- Automobile

- Amplificateur audio

- Unité principale

- ANC/RNC

- Divertissement pour siège arrière

- Cockpit numérique

- ADAS

- Grand public

- Systèmes audio-vidéo

- Consoles de mixage

- Réseaux de microphones

- Systèmes de conférence

Schéma de principe du processeur modèle complet

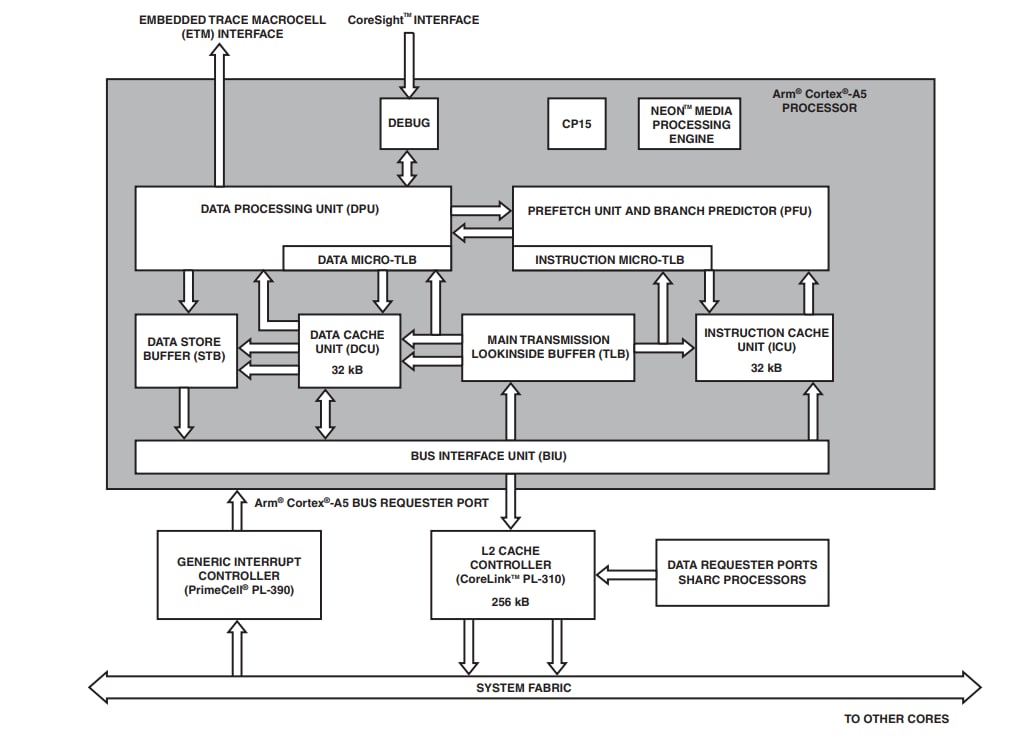

Schéma de principe du processeur Arm Cortex-A5

Schéma fonctionnel du processeur SHARC

Publié le: 2022-02-07

| Mis à jour le: 2025-10-01